Hire Verified & Experienced

FPGA design Tutors

4.8/5 40K+ session ratings collected on the MEB platform

Hire The Best FPGA design Tutor

Top Tutors, Top Grades. Without The Stress!

52,000+ Happy Students From Various Universities

How Much For Private 1:1 Tutoring & Hw Help?

Private 1:1 Tutoring and HW help Cost $20 – 35 per hour* on average.

Most students who struggle with FPGA design aren’t weak — they’ve never had someone explain why their state machine doesn’t synthesize.

FPGA Design Tutor Online

FPGA design is the process of programming field-programmable gate arrays using hardware description languages such as VHDL or Verilog, enabling engineers and students to implement custom digital logic circuits on reconfigurable silicon hardware.

MEB connects you with a verified FPGA design tutor online who knows Xilinx, Intel (Altera), and Lattice toolchains — and can work through your exact university module or industry project with you, live. If you’ve searched for an FPGA design tutor near me, online 1:1 sessions give you access to specialists your local area almost certainly doesn’t have. Tutors are matched to your HDL language, your FPGA family, and your current gaps — not assigned at random. Part of MEB’s wider electrical engineering tutoring offering, covering 2,800+ technical subjects since 2008.

- 1:1 online sessions tailored to your course syllabus or project spec

- Expert-verified tutors with hands-on FPGA synthesis and timing experience

- Flexible time zones — US, UK, Canada, Australia, Gulf

- Structured learning plan built after a diagnostic session

- Ethical homework and assignment guidance — you understand the work before you submit

52,000+ students across the US, UK, Canada, Australia, and the Gulf have used MEB since 2008 — including students in electrical engineering subjects like FPGA design, VHDL, and Verilog.

Source: My Engineering Buddy, 2008–2025.

How Much Does an FPGA Design Tutor Cost?

Most FPGA design tutoring sessions run $20–$40/hr. Graduate-level or industry-focused work — timing closure, high-speed interfaces, complex IP cores — can reach $70–$100/hr. Your first session is available for $1: 30 minutes of live tutoring or one assignment question explained in full.

| Level / Need | Typical Rate | What’s Included |

|---|---|---|

| Undergraduate (most modules) | $20–$40/hr | 1:1 sessions, VHDL/Verilog guidance, assignment support |

| Graduate / Advanced Design | $40–$70/hr | Timing analysis, IP integration, synthesis optimisation |

| Industry / Research-Level | $70–$100/hr | High-speed interfaces, DMA, partial reconfiguration |

| $1 Trial | $1 flat | 30 min live session or one full question explained |

Tutor availability tightens around final exam periods and end-of-semester project deadlines — book early if you’re working to a fixed date.

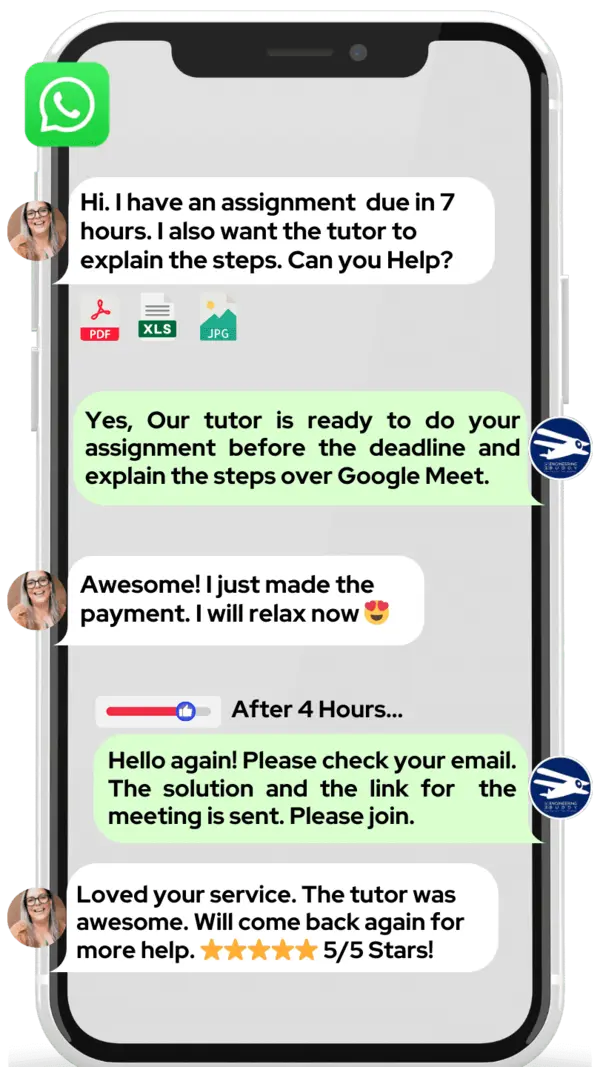

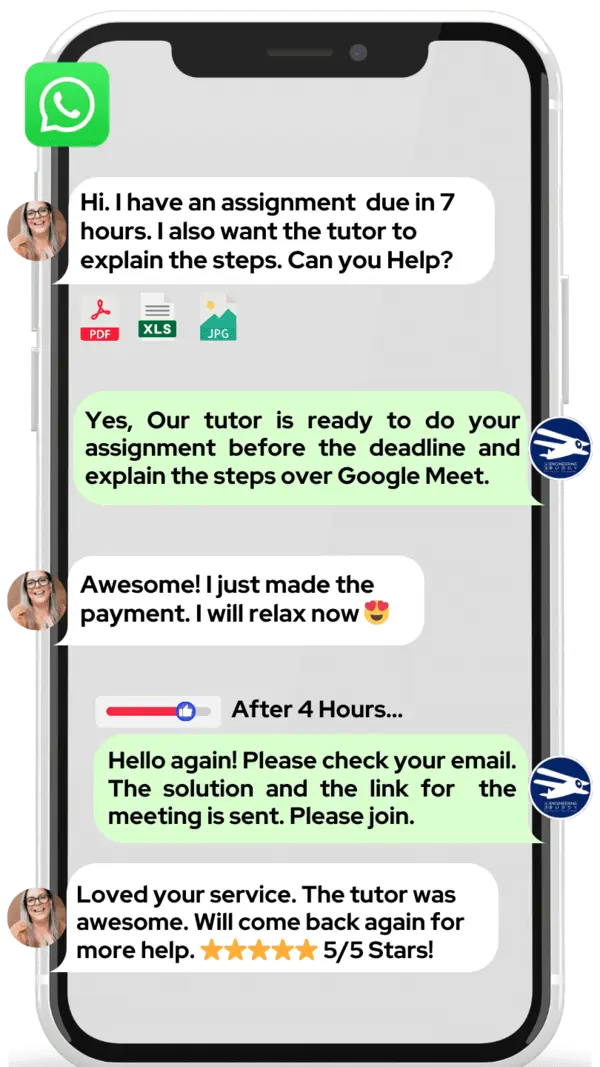

WhatsApp MEB for a quick quote — average response time under 1 minute.

Who This FPGA Design Tutoring Is For

FPGA design sits at the intersection of hardware thinking and software discipline. Students who struggle here usually aren’t failing at logic — they’re failing at the toolchain, the HDL syntax, or the gap between simulation and synthesis.

- Undergraduate EE or computer engineering students hitting their first digital design module

- Graduate students implementing custom processors, DSP pipelines, or communication systems on FPGA

- Students whose FPGA coursework compiles but doesn’t meet timing constraints — and they can’t figure out why

- Students retaking a failed digital design unit after losing marks on the implementation assignment

- Students with a university conditional offer dependent on passing their EE core modules this semester

- Parents watching a student’s confidence erode as their Vivado project runs into errors they can’t read

- Engineers transitioning from software to hardware who need structured FPGA fundamentals

Students come from universities across the US, UK, Canada, and Australia — including programs at MIT, Carnegie Mellon, Imperial College London, the University of Toronto, ETH Zürich, and TU Delft, among many others. The tutor matches to your exact syllabus, not a generic curriculum.

At MEB, we’ve found that the single biggest sticking point in FPGA design isn’t understanding logic — it’s the gap between what simulates correctly and what actually synthesizes. A tutor who’s been through that gap dozens of times can cut weeks off your debug time.

1:1 Tutoring vs Self-Study vs AI vs YouTube vs Online Courses

Self-study works if you’re disciplined, but FPGA toolchains throw cryptic errors that documentation rarely explains clearly. AI tools give fast answers — they can’t watch your constraint file, read your timing report, and tell you which path is failing. YouTube covers the basics well; it stops at “hello world” while your project needs AXI interfaces. Online courses are structured but fixed-pace with no one to unstick you at 11pm. 1:1 tutoring with MEB is live, calibrated to your exact module and toolchain, and corrects the actual error in front of you — not a generic version of it.

Outcomes: What You’ll Be Able To Do in FPGA Design

After working with an MEB FPGA design tutor, students consistently move from broken simulations to working hardware implementations. You’ll be able to write synthesisable VHDL or Verilog for combinational and sequential logic without guidance. You’ll be able to analyze timing reports in Vivado or Quartus Prime and identify critical path violations before they become submission failures. You’ll be able to implement state machines correctly — Moore and Mealy — and explain your design decisions in a viva or lab report. You’ll be able to apply clock domain crossing techniques and understand why metastability matters in real hardware. You’ll be able to present a working FPGA project — from RTL design through to bitstream generation — with confidence.

Based on feedback from 40,000+ sessions collected by MEB from 2022 to 2025, 58% of students improved by one full grade after approximately 20 hours of 1:1 tutoring in subjects like FPGA design. A further 23% achieved at least a half-grade improvement.

Source: MEB session feedback data, 2022–2025.

Supporting a student through FPGA design? MEB works directly with parents to set up sessions, track progress, and keep coursework on schedule. WhatsApp MEB — average response time is under a minute, 24/7.

Try your first session for $1 — 30 minutes of live 1:1 tutoring or one homework question explained in full. No registration. No commitment. WhatsApp MEB now and get matched within the hour.

What We Cover in FPGA Design (Syllabus / Topics)

Track 1: HDL Fundamentals and Digital Logic

- VHDL vs Verilog: syntax, structure, and when each is used

- Combinational logic: multiplexers, decoders, ALUs in HDL

- Sequential logic: D flip-flops, registers, shift registers

- Finite state machines: Moore vs Mealy, one-hot vs binary encoding

- Testbench writing and functional simulation in ModelSim or XSIM

- Understanding synthesis vs simulation discrepancies

- Common pitfalls: latches from incomplete sensitivity lists, blocking vs non-blocking assignments

Recommended texts: Digital Design and Computer Architecture by Harris & Harris (2nd ed.); Free Range VHDL by Bryan Mealy & Fabrizio Tappero.

Track 2: Synthesis, Constraints, and Timing Closure

- FPGA architecture: LUTs, flip-flops, block RAM, DSP slices, I/O banks

- Writing and applying XDC constraint files in Vivado

- Static timing analysis: setup time, hold time, slack interpretation

- Critical path identification and optimisation strategies

- Clock domain crossing and synchroniser design

- Pipelining for throughput improvement

- Partial reconfiguration concepts for advanced modules

Recommended texts: FPGA Prototyping by VHDL Examples by Pong P. Chu; The Design Warrior’s Guide to FPGAs by Clive Maxfield.

Track 3: System-Level Design and IP Integration

- AXI4 and AXI4-Lite bus protocols and interface design

- Using Vivado IP Integrator for block diagram-based design

- Soft processor integration: MicroBlaze or NIOS II basics

- DMA controllers and memory-mapped peripherals

- High-speed serial interfaces: UART, SPI, I2C on FPGA

- DSP on FPGA: FIR filters, FFT pipelines using DSP blocks

- Interfacing with embedded systems and external memory

Recommended texts: Digital Design with RTL Design, VHDL, and Verilog by Frank Vahid; FPGA-Based System Design by Wayne Wolf.

MEB tutors cover Xilinx (AMD) Vivado, Intel Quartus Prime, and Lattice Diamond — matched to whichever toolchain your course or employer uses. Sessions run on the tools you’re actually being assessed on.

Source: My Engineering Buddy, 2008–2025.

Platforms, Tools & Textbooks We Support

FPGA design is entirely toolchain-dependent. Tutors work inside the environment your course requires — not a generic simulation environment. Supported platforms include:

- AMD/Xilinx Vivado Design Suite (all versions)

- Intel Quartus Prime (Lite, Standard, Pro)

- Lattice Diamond and Radiant

- ModelSim / QuestaSim for functional simulation

- MATLAB/Simulink HDL Coder for model-based FPGA design

- Xilinx Vitis for HLS (High-Level Synthesis) workflows

- NIST engineering standards for interface compliance — see NIST Engineering Laboratory for reference documentation

What a Typical FPGA Design Session Looks Like

The tutor starts by checking where you got stuck since the last session — often a synthesis error in a state machine or a timing constraint that refused to close. You screen-share your Vivado or Quartus project directly. The tutor reads your timing report with you, points to the failing path, and explains exactly which line of your HDL is causing it. They write a corrected version on their digital pen-pad while you follow along, then you replicate the fix yourself and re-run synthesis. By the end of the session, you have a working or significantly improved design — and a concrete task list for the next 48 hours, usually centred on completing the testbench or writing the constraint file for the next module.

How MEB Tutors Help You with FPGA Design (The Learning Loop)

Diagnose: In the first session, the tutor asks you to walk through a recent design or error. They identify immediately whether the gap is in your HDL syntax, your understanding of the underlying hardware architecture, your constraint methodology, or all three. That shapes every session that follows.

Explain: The tutor works through a live example on a digital pen-pad — writing VHDL or Verilog from scratch, annotating the timing diagram, or tracing the synthesis output back to your source code. You watch it built, not described.

Practice: You attempt the next problem — write the FSM, close the timing, implement the AXI interface — with the tutor watching. They don’t jump in early. They let you think through it and note where you hesitate.

Feedback: After you attempt it, the tutor goes through each decision point: why that encoding choice costs more LUTs, why that sensitivity list creates a latch, what the timing report is telling you and how to respond. Specific, line-by-line, no vague encouragement.

Plan: Every session ends with a clear next topic and a specific task — “implement a 4-bit counter with synchronous reset and verify it meets a 100MHz timing constraint.” Progress is tracked between sessions.

Sessions run over Google Meet. The tutor uses a digital pen-pad or iPad with Apple Pencil for annotating waveforms, drawing state diagrams, and marking up HDL. Before your first session, share your syllabus or project spec, your current Vivado/Quartus project file, and your exam or deadline date. The first session covers a diagnostic and usually resolves one concrete blocking issue. Start with the $1 trial — 30 minutes of live tutoring that also functions as your first diagnostic.

Students consistently tell us that the moment things click in FPGA design is when they see their own HDL annotated in real time — not explained in the abstract, but rewritten line by line with the reasoning shown alongside it. That’s what a pen-pad session does that a video lecture never can.

Tutor Match Criteria (How We Pick Your Tutor)

Not every electrical engineering tutor knows FPGA design. MEB matches on specifics.

Subject depth: Tutors are vetted on the HDL language your course uses (VHDL, Verilog, or SystemVerilog), the FPGA family and toolchain in your syllabus, and the level — undergraduate module, graduate research, or industry project.

Tools: Every session runs on Google Meet. Tutors use a digital pen-pad or iPad and Apple Pencil so timing diagrams, state charts, and HDL annotations are drawn live, not described verbally.

Time zone: Matched to your region — US, UK, Gulf, Canada, or Australia. Late-night sessions are available; the tutor roster covers all major time zones.

Goals: Whether you need to pass one specific module, complete a final-year project, or build foundational HDL skills for an employer, the tutor match reflects that goal — not a one-size-fits-all assignment.

Unlike platforms where you fill out a form and wait, MEB responds in under a minute, 24/7. Tutor match takes under an hour. The $1 trial means you test before you commit. Everything runs over WhatsApp — no logins, no intake forms.

Study Plans (Pick One That Matches Your Goal)

The tutor builds your session sequence after the first diagnostic, but most FPGA design students fall into one of three plans. Catch-up (1–3 weeks): you’re behind on HDL fundamentals or a specific module component and need to close the gap before an assessment. Exam and project prep (4–8 weeks): structured sessions aligned to your submission or exam date, covering synthesis, timing, and implementation in sequence. Weekly support: ongoing 1:1 sessions running parallel to your semester, tied to each week’s lab or lecture content. The tutor adjusts the sequence after every session based on what you’ve retained and what’s still shaky.

Pricing Guide

FPGA design tutoring starts at $20/hr for undergraduate modules. Graduate-level work — SoC design, HLS flows, advanced timing closure — typically runs $50–$70/hr. Research-level or industry-specification support can reach $100/hr. Rate factors include your module level, the complexity of the toolchain in scope, your timeline, and tutor availability during peak periods.

Availability tightens significantly during final exam windows and end-of-semester project deadlines. If you have a fixed submission date, book sooner rather than later.

For students targeting placements at semiconductor firms, defence contractors, or postgraduate research programs, MEB has tutors with professional FPGA engineering backgrounds available at higher rates — share your goal and MEB matches the tier to your ambition.

Start with the $1 trial — 30 minutes, no registration, no commitment. WhatsApp MEB for a quick quote.

FAQ

Is FPGA design hard?

It’s genuinely difficult. You’re learning to think in concurrent hardware execution, not sequential software. Most students find the switch from software mindset to hardware mindset the hardest part — followed closely by reading synthesis errors and timing reports without guidance.

How many sessions are needed?

Students closing specific gaps before an assignment typically need 4–8 sessions. Those building from foundational HDL through to system-level design over a semester average 15–20 sessions. The tutor sets a realistic estimate after the first diagnostic.

Can you help with FPGA homework and assignments?

MEB tutoring is guided learning — you understand the work, then submit it yourself. The tutor explains the concept, works through a related example, and then you apply it independently. See our Academic Integrity policy and Why MEB page for full details on what we help with and what we don’t.

Will the tutor match my exact syllabus or exam board?

Yes. Tutors are matched to your specific university module, HDL language (VHDL, Verilog, SystemVerilog), toolchain (Vivado, Quartus, Lattice), and level. MEB does not assign a generic digital design tutor to an FPGA-specific module.

What happens in the first session?

The tutor runs a diagnostic — reviewing your current project, recent errors, or past assignment feedback. They identify your three biggest gaps and begin on the most urgent one immediately. You leave the first session with a clear picture of what’s blocking you and why.

Is online FPGA tutoring as effective as in-person?

For FPGA work, online is often better. You screen-share your actual Vivado or Quartus project. The tutor sees the real error, the real timing report, and the real HDL — not a whiteboard approximation. The digital pen-pad adds the visual layer that screen-sharing alone misses.

What’s the difference between VHDL and Verilog, and does it matter which I learn?

Both describe the same hardware; syntax and style differ significantly. VHDL is more common in European and aerospace/defence contexts; Verilog and SystemVerilog dominate in US industry and ASIC design. Your course or employer usually specifies one. MEB tutors cover both — and SystemVerilog for advanced work.

My design simulates correctly but fails after synthesis — can a tutor help with that?

This is one of the most common FPGA problems MEB tutors solve. Simulation-synthesis mismatches usually stem from non-synthesisable constructs, incomplete sensitivity lists, or clock domain issues. A tutor can identify the cause in a single session in most cases.

Can I get FPGA design help at midnight?

Yes. MEB operates across all major time zones, 24/7. WhatsApp MEB at any hour — average response time is under one minute. Tutors in matching time zones are available for late-night sessions, including the nights before submission deadlines.

What if I don’t like my assigned tutor?

Request a switch over WhatsApp. MEB reassigns without friction. The $1 trial is specifically designed so you test the match before committing to a paid schedule — most students confirm their tutor after the first session.

Do you cover HLS (High-Level Synthesis) and Vitis?

Yes. Tutors cover Xilinx Vitis HLS for C/C++ to RTL flows, including pragma-based optimisation for throughput and latency. This is increasingly part of graduate and industry FPGA modules, and MEB has tutors who work with it professionally.

How do I get started?

WhatsApp MEB, share your module, toolchain, and deadline. You’re matched with a verified tutor — usually within the hour. The $1 trial is your first step: 30 minutes of live 1:1 tutoring, or one assignment question explained in full, for $1.

Trust & Quality at My Engineering Buddy

Every MEB tutor passes a multi-stage screening process: subject knowledge assessment, a live demo session, and ongoing review based on student feedback after every session. FPGA design tutors hold degrees in electrical engineering, computer engineering, or a related hardware discipline — and most have hands-on industry or research experience with real FPGA deployments, not just academic familiarity. Rated 4.8/5 across 40,000+ verified reviews on Google. You can read more about how MEB selects and vets tutors on the MEB tutoring methodology page.

MEB tutoring is guided learning — you understand the work, then submit it yourself. For full details on what we help with and what we don’t, read our Academic Integrity policy and Why MEB.

MEB has served 52,000+ students across the US, UK, Canada, Australia, the Gulf, and Europe since 2008 — across electrical engineering subjects including digital electronics tutoring, VLSI design help, and digital signal processing tutoring. The platform covers 2,800+ technical subjects, all delivered 1:1.

MEB has operated since 2008. That’s 17 years of refining what works in technical tutoring — including for hardware subjects like FPGA design where the toolchain changes but the fundamentals of good teaching don’t.

Source: My Engineering Buddy, 2008–2025.

Explore Related Subjects

Students studying FPGA design often also need support in:

- VHDL

- Verilog

- Digital Circuit

- Microprocessors

- Integrated Circuits (IC)

- Signals and Systems

- Semiconductor Devices

Next Steps

Getting started takes about two minutes over WhatsApp.

- Share your course module, HDL language, toolchain, and current sticking point

- Share your availability and time zone

- MEB matches you with a verified FPGA design tutor — usually within the hour

- The first session starts with a diagnostic so every minute is used on your actual gaps

Before your first session, have ready: your university module outline or project specification, a recent HDL file or error log you’ve been stuck on, and your exam or submission deadline date. The tutor handles the rest.

Visit www.myengineeringbuddy.com for more on how MEB works.

WhatsApp to get started or email meb@myengineeringbuddy.com.

A common pattern our tutors observe is that students who spend one focused session on timing analysis and constraint methodology stop producing synthesis failures entirely within a week. Understanding the toolchain’s feedback is the unlock — and that’s exactly what the first few sessions build.

Reviewed by Subject Expert

This page has been carefully reviewed and validated by our subject expert to ensure accuracy and relevance.