Hire The Best VHDL Tutor

Top Tutors, Top Grades. Without The Stress!

52,000+ Happy Students From Various Universities

How Much For Private 1:1 Tutoring & Hw Help?

Private 1:1 Tutoring and HW help Cost $20 – 35 per hour* on average.

Most VHDL students hit the same wall: the syntax looks fine, the simulation runs, but the hardware won’t synthesize — and nobody explains why.

VHDL Tutor Online

VHDL (VHSIC Hardware Description Language) is a hardware description language used to model and design digital systems at RTL and gate level, enabling simulation, verification, and FPGA or ASIC synthesis for embedded and digital circuit applications.

If you’ve searched for a VHDL tutor near me, the honest answer is that the best VHDL help is online — because the tutors who genuinely know RTL design, FPGA synthesis, and testbench verification are rarely local. MEB has matched students across electrical engineering courses with verified VHDL tutors since 2008. You won’t get a generalist who learned VHDL last week — you’ll get someone who has debugged timing failures and written synthesis-ready code professionally.

- 1:1 online sessions tailored to your exact course, university module, or project brief

- Expert-verified tutors with hands-on FPGA, ASIC, and digital design backgrounds

- Flexible time zones — US, UK, Canada, Australia, Gulf covered

- Structured learning plan built after a diagnostic session

- Ethical homework and assignment guidance — you understand the work before you submit it

52,000+ students across the US, UK, Canada, Australia, and the Gulf have used MEB since 2008 — including students in Electrical Engineering subjects like VHDL, FPGA design, and digital electronics.

Source: My Engineering Buddy, 2008–2025.

How Much Does a VHDL Tutor Cost?

Most VHDL sessions run $20–$40/hr. Graduate-level RTL design, ASIC flows, or FPGA timing closure work can reach $60–$100/hr depending on the tutor’s industry background. The $1 trial gives you 30 minutes of live 1:1 tutoring — no registration, no commitment.

| Level / Need | Typical Rate | What’s Included |

|---|---|---|

| Undergraduate (most modules) | $20–$40/hr | 1:1 sessions, assignment guidance |

| Advanced / FPGA / ASIC | $40–$100/hr | Expert tutor, synthesis & timing depth |

| $1 Trial | $1 flat | 30 min live session or 1 assignment question |

FPGA project deadlines and end-of-semester lab submissions drive tutor demand up sharply. Availability in peak periods is limited — book early.

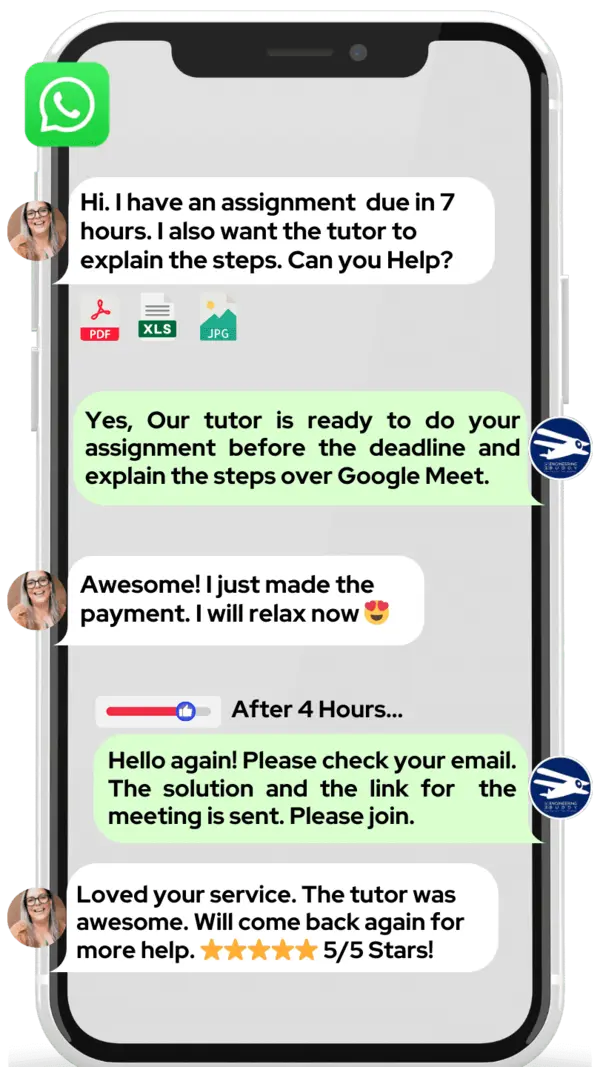

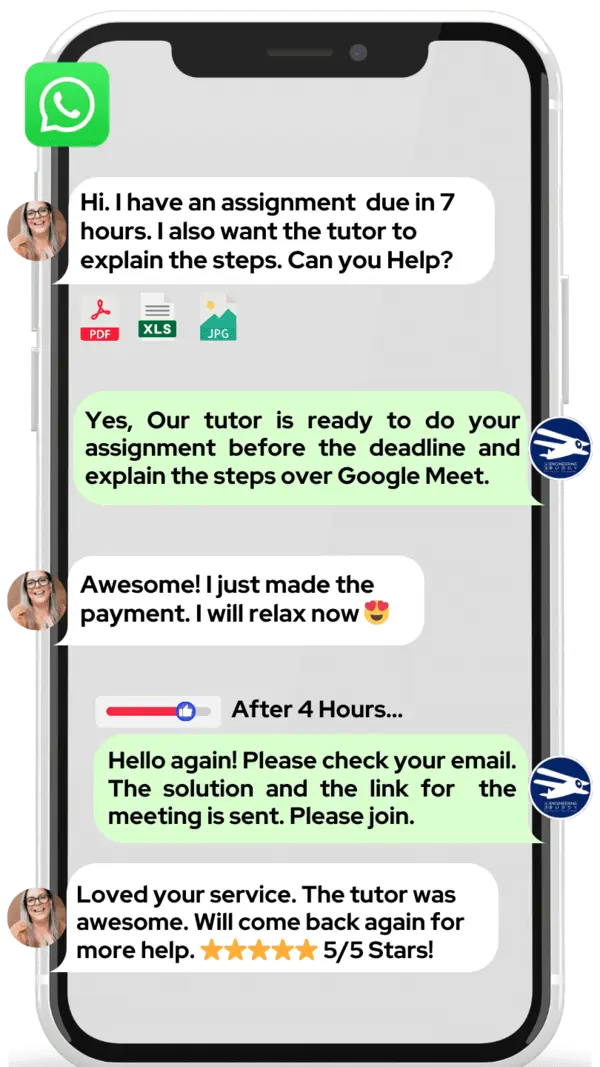

WhatsApp MEB for a quick quote — average response time under 1 minute.

Who This VHDL Tutoring Is For

VHDL sits in a difficult spot — taught in electrical engineering and computer engineering programmes, but treated as a secondary skill in many departments. Most students get two weeks of lecture slides and then face a 30% project. If that’s you, you’re not behind because you’re slow — you’re behind because the teaching didn’t match the assessment.

- Undergraduate EE or CE students in digital design, computer architecture, or embedded systems modules

- Students who failed or narrowly passed their first VHDL lab and need to close the gap before finals

- Students retaking after a failed first attempt — the tutor starts from your specific sticking point, not from scratch

- Master’s students using VHDL in RTL design, signal processing cores, or thesis-related FPGA implementation

- Engineers upskilling into FPGA or ASIC roles who need structured, project-grounded VHDL practice

- Parents supporting a student whose confidence in digital circuits has dropped alongside their grades

Students from programmes at institutions including MIT, Georgia Tech, Imperial College London, TU Delft, University of Toronto, ETH Zürich, and KFUPM have worked with MEB tutors on VHDL coursework and projects. Start with the $1 trial — it also works as your first diagnostic session.

At MEB, we’ve found that VHDL students often know what they want the circuit to do — they just haven’t yet built the mental model that separates concurrent signal assignment from sequential process logic. That gap closes faster than most students expect once you work through it live with someone who designs hardware for real.

1:1 Tutoring vs Self-Study vs AI vs YouTube vs Online Courses

Each option has a ceiling when it comes to VHDL.

Self-study works if you have time and the right textbooks — but there’s no one to catch a wrong mental model before it compounds. AI tools will generate syntactically valid VHDL that won’t synthesize — and won’t tell you why. YouTube covers basic combinational logic well; it stops short the moment you need to debug a timing failure or understand clock domain crossing. Online courses move at a fixed pace and rarely match your university’s specific synthesis toolchain. 1:1 tutoring with MEB is live, calibrated to your exact module or project, and corrects errors in the moment — particularly the RTL-versus-behavioral distinction that trips up most students in assessed work.

Outcomes: What You’ll Be Able To Do in VHDL

After working with an MEB VHDL tutor, most students can write and simulate both combinational and sequential VHDL designs with confidence. You’ll be able to model finite state machines correctly in both Mealy and Moore forms, write synthesis-ready RTL code that passes timing analysis in tools like Vivado or Quartus, and build structured testbenches with self-checking assertions. You’ll understand what makes a design synthesizable versus simulation-only — a distinction that costs marks on almost every VHDL assessment. You’ll also be able to read and interpret a timing report and explain your design decisions clearly in a lab report or viva.

Based on feedback from 40,000+ sessions collected by MEB from 2022 to 2025, 58% of students improved by one full grade after approximately 20 hours of 1:1 tutoring in subjects like VHDL. A further 23% achieved at least a half-grade improvement.

Source: MEB session feedback data, 2022–2025.

Supporting a student through VHDL? MEB works directly with parents to set up sessions, track progress, and keep coursework on schedule. WhatsApp MEB — average response time is under a minute, 24/7.

What We Cover in VHDL (Syllabus / Topics)

Track 1: VHDL Fundamentals and Combinational Design

- VHDL language structure: entities, architectures, and packages

- Data types: std_logic, std_logic_vector, integer, and enumeration types

- Concurrent signal assignment: when/else, with/select, and direct assignment

- Combinational logic design: multiplexers, decoders, encoders, and arithmetic units

- Structural modeling with component instantiation and port mapping

- Simulation basics: running a waveform in ModelSim or GHDL

- Common synthesis pitfalls: incomplete sensitivity lists, latches vs. registers

Recommended texts: VHDL Programming by Example by Douglas Perry; Digital Design Using VHDL by William Dally and R. Curtis Harting.

Track 2: Sequential Logic and Finite State Machines

- Process statements: sensitivity lists, wait statements, and clocked processes

- D flip-flops, registers, and synchronous vs. asynchronous reset conventions

- Mealy and Moore FSM architectures: single-process and two-process templates

- State encoding: binary, one-hot, and Gray code — synthesis implications

- Counters, shift registers, and sequence detectors

- Clock domain crossing basics and synchronizer circuits

- Testbench design for sequential systems: clock generation, stimulus files

Recommended texts: VHDL for Logic Synthesis by Andrew Rushton; Free Range VHDL (open access) by Bryan Mealy and Fabrizio Tappero.

Track 3: RTL Design, FPGA Synthesis, and Verification

- RTL design methodology: datapath and control unit separation

- Synthesis constraints: timing, area, and power trade-offs in Vivado and Quartus

- Post-synthesis and post-implementation simulation

- Timing analysis: setup and hold violations, critical path identification

- FPGA-specific constructs: block RAM inference, DSP slice targeting

- UVM-lite and self-checking testbench patterns for verification

- Integration with Verilog mixed-language projects and IP core instantiation

Recommended texts: Digital Design and Computer Architecture by David Harris and Sarah Harris; FPGA Prototyping by VHDL Examples by Pong P. Chu.

Platforms, Tools & Textbooks We Support

VHDL tutoring at MEB covers the full tool stack used in university programmes and industry. Tutors are familiar with simulation environments including ModelSim, GHDL, and Active-HDL; synthesis tools including AMD/Xilinx Vivado and Intel/Altera Quartus Prime; and development boards including the Basys 3, Nexys A7, and DE10 series. Sessions can also cover digital signal processing implementation in VHDL and IP integration workflows.

- ModelSim / QuestaSim

- GHDL + GTKWave

- Xilinx Vivado

- Intel Quartus Prime

- Active-HDL (Aldec)

- Basys 3, Nexys A7, DE10-Lite development boards

- MATLAB/Simulink HDL Coder (for co-simulation)

What a Typical VHDL Session Looks Like

The tutor opens by checking where you got stuck since the last session — usually a specific line in your process statement or a failed synthesis report. You’ll share your screen and work through the problem together: the tutor might take over with a digital pen-pad to annotate your code directly, showing you exactly why a sensitivity list is generating a latch or why your FSM state transitions aren’t registering. Then you attempt the corrected version yourself while the tutor watches. Towards the end, the tutor sets a concrete task — write a counter with synchronous reset and run it in ModelSim — and notes the next topic, usually timing constraints or testbench structure, for the following session.

How MEB Tutors Help You with VHDL (The Learning Loop)

Diagnose: In the first session, the tutor asks you to walk through a piece of VHDL you’ve already written. This reveals whether your mental model of concurrency is correct, which data types you’re reaching for instinctively, and where your simulation-vs-synthesis boundary sits. It takes about 15 minutes and tells the tutor more than a syllabus document ever could.

Explain: The tutor works through a live example — not a textbook example, but one matched to your assignment or project brief. Using a digital pen-pad on Google Meet, they annotate directly: signal flow, clock edges, process priority. You see the reasoning in real time, not just the solution.

Practice: You attempt the next problem with the tutor present. Not watching quietly — actively prompting. “What happens to that signal on the next rising edge?” The pressure is low; the feedback is immediate.

Feedback: The tutor identifies exactly where your reasoning broke down. Not “this is wrong” — but “you’ve treated this as a concurrent assignment when it needs to be inside the clocked process — here’s why that matters for synthesis.” Marks are lost at specific reasoning steps. The tutor names them.

Plan: Before the session ends, the tutor notes what you covered, what to practice before next time, and which topic comes next. You leave with a task, not just a feeling that it went well.

Sessions run on Google Meet with a digital pen-pad or iPad and Apple Pencil for annotation. Before your first session, have your module specification or project brief ready, plus any code you’ve already written and the error messages or simulation output you’re stuck on. Start with the $1 trial — 30 minutes of live tutoring that doubles as your first diagnostic.

Try your first session for $1 — 30 minutes of live 1:1 tutoring or one homework question explained in full. No registration. No commitment. WhatsApp MEB now and get matched within the hour.

Tutor Match Criteria (How We Pick Your Tutor)

Not every engineer who knows VHDL can teach it. MEB’s match process filters on four things.

Subject depth: The tutor must have worked with VHDL at the level you need — undergraduate synthesis, graduate RTL design, or professional FPGA implementation. A tutor who only knows behavioral simulation won’t be matched to a student doing timing closure work.

Tools: Your tutor uses Google Meet plus a digital pen-pad or iPad with Apple Pencil so code annotation is live and visible. No static slides.

Time zone: Matched to your region — US, UK, Gulf, Canada, or Australia — so sessions happen when you actually study, not at 3 a.m.

Goals: Whether you need to pass a lab exam, complete an FPGA project, or build research-grade RTL for a thesis, the tutor is matched to that specific goal — not assigned randomly from a roster.

Unlike platforms where you fill out a form and wait days, MEB responds in under a minute, 24/7. Tutor match takes under an hour. The $1 trial means you test before you commit. Everything runs over WhatsApp — no logins, no intake forms.

Study Plans (Pick One That Matches Your Goal)

A single diagnostic session tells the tutor which plan fits. For students 1–3 weeks from a lab deadline, the focus is gap-closing: get the specific design working and submission-ready. For students 4–8 weeks from finals, the plan builds systematically from combinational to sequential to RTL to testbench. For ongoing semester support, sessions align to your module schedule — one topic per week, with problem sets reviewed before each session. The tutor maps the exact sequence after the diagnostic; you don’t need to figure out the order yourself.

Pricing Guide

VHDL tutoring starts at $20/hr for standard undergraduate modules. Graduate-level RTL design and FPGA timing work sits at $40–$100/hr depending on the tutor’s industry experience. Rate factors include your level, the complexity of the synthesis tool you’re using, your timeline, and tutor availability in your time zone.

FPGA project submission periods and end-of-semester exams reduce available slots quickly. If you’re within four weeks of a deadline, don’t wait.

For students targeting roles at semiconductor companies or research positions requiring advanced RTL skills, tutors with professional ASIC and FPGA industry backgrounds are available at higher rates — share your specific goal and MEB will match the tier to your target.

Start with the $1 trial — 30 minutes, no registration, no commitment. WhatsApp MEB for a quick quote.

MEB has covered digital circuit design, embedded systems, and VHDL for students at undergraduate through research level since 2008 — across 2,800+ subjects in engineering and applied sciences.

Source: My Engineering Buddy, 2008–2025.

FAQ

Is VHDL hard?

VHDL has a steep initial curve because hardware description is fundamentally different from software programming. Concurrency, signal assignment semantics, and the simulation-versus-synthesis gap trip up most beginners. With a tutor working through your specific code, most students stabilize within 4–6 sessions.

How many sessions are needed?

Students with a specific lab or assignment deadline typically need 3–5 focused sessions. Students building competence across a full VHDL module usually need 8–15 sessions over a semester. The tutor sets a realistic target after the first diagnostic.

Can you help with VHDL homework and assignments?

Yes — MEB tutoring is guided learning. The tutor explains the concepts and works through examples with you; you then produce and submit the work yourself. See our Academic Integrity policy and Why MEB page for full details on what we help with and what we don’t.

Will the tutor match my exact syllabus or exam board?

Yes. Before the first session, share your module outline, the synthesis tool your university uses (Vivado, Quartus, etc.), and your assessment brief. The tutor adapts entirely to your specific course requirements — not a generic VHDL curriculum.

What happens in the first session?

The tutor starts with a short diagnostic — you walk through existing code or attempt a short problem while the tutor observes. Within 20 minutes, they know your exact gaps and can plan the session sequence. No time is spent on topics you already understand.

Is online VHDL tutoring as effective as in-person?

For VHDL, online is often better. Screen sharing lets the tutor annotate your actual code directly; a digital pen-pad shows signal timing and FSM diagrams in real time. You’re not looking at a whiteboard from across a table — you’re looking at your own work being explained.

What’s the difference between behavioral, RTL, and structural VHDL — and which one does my course actually test?

Most undergraduate assessments test RTL and structural modeling, though behavioral is taught first. RTL is what synthesizes to real hardware. Your tutor will identify which abstraction level your assignment targets and make sure your code is written at the right level for the marks available.

Can a VHDL tutor help me if I also need to learn Verilog for the same project?

Yes. Many MEB tutors cover both VHDL and Verilog. Mixed-language projects are common in industry and in some university modules. Tell MEB at the start and the tutor will be matched to cover both HDLs within your project scope.

Do you offer help for FPGA implementation, not just simulation?

Yes — this is one of MEB’s stronger areas in VHDL. Tutors can cover full Vivado or Quartus flows: synthesis, implementation, constraint writing, and timing closure. Simulation-only tutors are filtered out when the student’s goal includes working on real hardware.

Can I get VHDL help at short notice — same day or late at night?

MEB operates 24/7 via WhatsApp. Tutors span multiple time zones, so late-night sessions in the US, UK, or Gulf are routinely available. Same-day matching is typical outside peak submission periods; response to your first message averages under one minute.

How do I get started?

Three steps: WhatsApp MEB, share your course and goal, and book the $1 trial — 30 minutes of live 1:1 tutoring or one assignment question explained in full. You’re matched with a tutor and into a session usually within the hour.

Students consistently tell us that the moment VHDL clicks is when they stop thinking in lines of code and start thinking in hardware — signals that exist simultaneously, not instructions that execute in order. That shift happens faster in a live session than it ever does reading documentation alone.

Trust & Quality at My Engineering Buddy

Every MEB tutor goes through subject-specific vetting: a credential check, a live demo session evaluated against known benchmarks, and ongoing review based on student session feedback. Tutors covering VHDL are assessed on RTL design accuracy, testbench construction, and synthesis tool familiarity — not just general electronics knowledge. Rated 4.8/5 across 40,000+ verified reviews on Google, MEB has been running since 2008 across 2,800+ subjects including VLSI design and computer engineering. Read more about our tutoring methodology.

MEB tutoring is guided learning — you understand the work, then submit it yourself. For full details on what we help with and what we don’t, read our Academic Integrity policy and Why MEB.

MEB serves students in the US, UK, Canada, Australia, the Gulf, and across Europe. In Electrical Engineering specifically, the platform covers VHDL alongside integrated circuits and signals and systems — from first-year fundamentals through graduate research-level work.

A common pattern our tutors observe is that VHDL students who struggle with synthesis haven’t been told explicitly that simulation and synthesis are governed by different subsets of the language. Once that’s clear, the rest of the debugging process becomes far more logical — and far less frustrating.

Explore Related Subjects

Students studying VHDL often also need support in:

- Analog Circuits

- Microcontrollers

- Microprocessors

- Logic Gates

- Circuit Design

- Semiconductor Devices

- Control Systems

Next Steps

Before your first session, have ready: your module outline or project brief, the synthesis tool your university uses, any VHDL code you’ve written so far, and your submission or exam date. The tutor handles the rest.

- Share your exam board or module details, the specific topic causing problems, and your timeline

- Share your availability and time zone

- MEB matches you with a verified VHDL tutor — usually within the hour

Visit www.myengineeringbuddy.com for more on how MEB works.

WhatsApp to get started or email meb@myengineeringbuddy.com.

Reviewed by Subject Expert

This page has been carefully reviewed and validated by our subject expert to ensure accuracy and relevance.