Hire The Best Verilog Tutor

Top Tutors, Top Grades. Without The Stress!

52,000+ Happy Students From Various Universities

How Much For Private 1:1 Tutoring & Hw Help?

Private 1:1 Tutoring and HW help Cost $20 – 35 per hour* on average.

Your Verilog testbench compiles — but the simulation waveform makes no sense, and the lab report is due in 48 hours.

Verilog Tutor Online

Verilog is a hardware description language (HDL) used to model, simulate, and synthesise digital circuits — from combinational logic to complex finite state machines — targeting FPGA and ASIC implementation at undergraduate and graduate level.

Finding a Verilog tutor near me who actually understands RTL design, synthesis constraints, and simulation debugging — not just the syntax — is harder than it sounds. MEB has matched students across electrical engineering with verified Verilog tutors since 2008. Sessions are live, 1:1, and built around your exact course, simulator, and deadline. One tutor. Your syllabus. No guesswork.

- 1:1 online sessions tailored to your specific course, simulator, and lab assignments

- Expert-verified tutors with hands-on RTL design, FPGA, and ASIC experience

- Flexible time zones — US, UK, Canada, Australia, Gulf covered

- Structured learning plan built after a diagnostic session

- Ethical homework and assignment guidance — you understand the work, then submit it yourself

52,000+ students across the US, UK, Canada, Australia, and the Gulf have used MEB since 2008 — including students in Electrical Engineering subjects like Verilog, VHDL, and FPGA design.

Source: My Engineering Buddy, 2008–2025.

How Much Does a Verilog Tutor Cost?

Most Verilog sessions run $20–$40/hr. Graduate-level RTL design, synthesis optimisation, or ASIC-targeted coursework can reach $70–$100/hr depending on tutor depth and timeline urgency. New students start with a $1 trial — 30 minutes of live 1:1 tutoring or one homework question explained in full.

| Level / Need | Typical Rate | What’s Included |

|---|---|---|

| Undergraduate (intro HDL) | $20–$35/hr | 1:1 sessions, lab and homework guidance |

| Advanced / RTL & FPGA | $35–$70/hr | Expert tutor, synthesis and timing closure |

| Graduate / ASIC-level | $70–$100/hr | Research-grade support, HDL for tapeout projects |

| $1 Trial | $1 flat | 30 min live session or 1 homework question explained |

Tutor availability tightens significantly in the weeks before end-of-semester lab submissions and final exams. Book early if you’re working to a hard deadline.

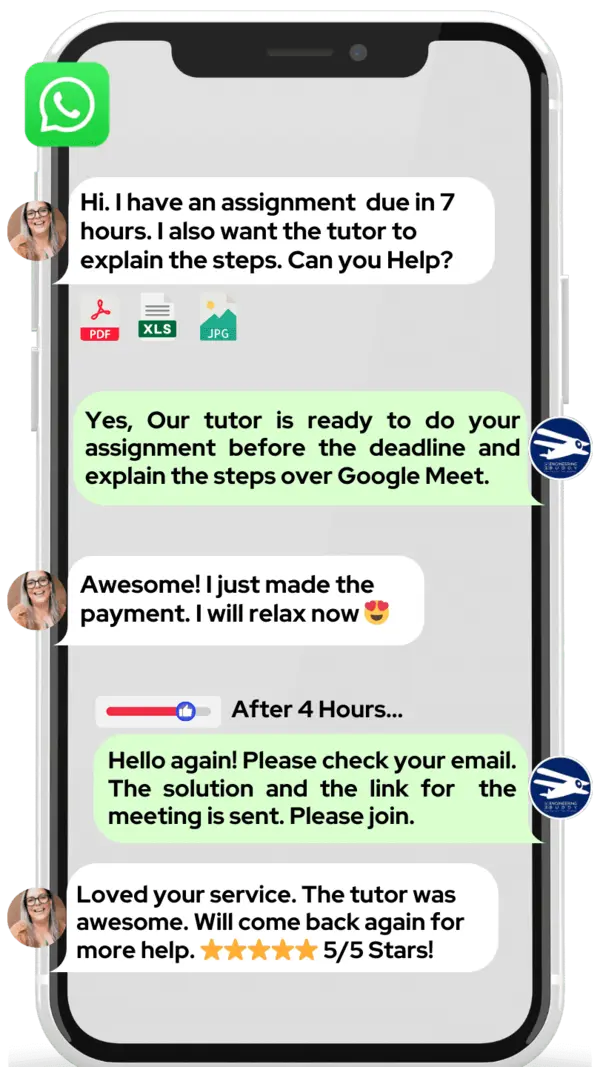

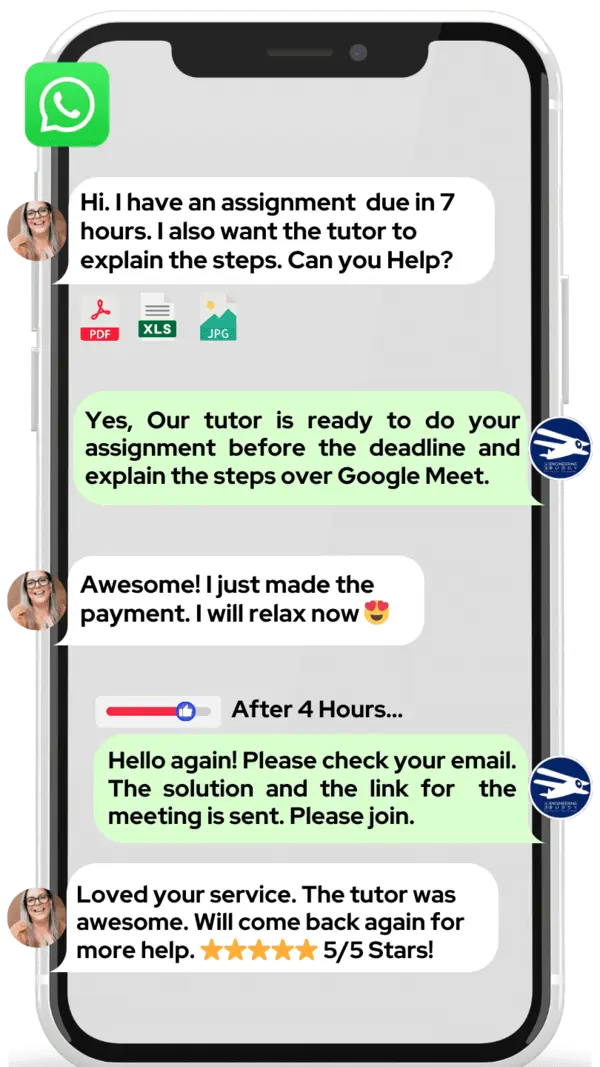

WhatsApp MEB for a quick quote — average response time under 1 minute.

Who This Verilog Tutoring Is For

Verilog trips people up at every level. The syntax looks approachable until concurrency, blocking vs non-blocking assignments, and simulation mismatches hit at the same time. These sessions are for students who need someone to work through the real problems — not just read slides at them.

- Undergraduate EE and computer engineering students in their first HDL module

- Students whose simulation waveforms do not match expected RTL behaviour

- Students retaking a digital design course after a failed first attempt

- Graduate students building Verilog-based FPGA or ASIC projects for coursework or thesis

- Students at MIT, Carnegie Mellon, Georgia Tech, Purdue, UC San Diego, University of Toronto, and Imperial College London where HDL design is a core requirement

- Anyone working with Xilinx Vivado or Intel Quartus who needs live debugging support, not just documentation

Not sure if this fits your level? The $1 trial session also acts as a diagnostic — you’ll know within 30 minutes whether the tutor and approach are right for you.

1:1 Tutoring vs Self-Study vs AI vs YouTube vs Online Courses

Self-study works if you’re disciplined — but Verilog errors in simulation are notoriously hard to diagnose alone. AI tools explain syntax fast but can’t watch your waveform and tell you why your FSM is misbehaving. YouTube is good for introductory walkthroughs and stops the moment your specific testbench fails. Online courses move at a fixed pace and never adapt when your lab assignment diverges from the lecture examples. With a 1:1 Verilog tutor from MEB, the tutor sees your actual code, your simulator output, and your assignment spec — and fixes the real problem, live, in the session.

Outcomes: What You’ll Be Able To Do in Verilog

After consistent 1:1 sessions, students leave with capabilities that hold up under exam and lab pressure — not just surface familiarity. You’ll be able to write synthesisable RTL for combinational and sequential circuits without relying on templates. You’ll analyse simulation waveforms in ModelSim or Vivado and identify the exact clock edge or signal assignment causing unexpected behaviour. You’ll model finite state machines correctly using Moore and Mealy architectures, and explain the timing implications of each. Apply testbench writing techniques to verify your own designs before submission. Present your design’s resource utilisation and timing report to a supervisor with confidence.

Based on feedback from 40,000+ sessions collected by MEB from 2022 to 2025, 58% of students improved by one full grade after approximately 20 hours of 1:1 tutoring in subjects like Verilog. A further 23% achieved at least a half-grade improvement.

Source: MEB session feedback data, 2022–2025.

At MEB, we’ve found that most Verilog students struggle not with the language itself but with the gap between writing code and understanding what the simulator is actually telling them. That’s almost always the first thing a tutor addresses — and the shift in confidence that follows is immediate.

What We Cover in Verilog (Syllabus / Topics)

Track 1: Foundations of HDL and Digital Logic in Verilog

- Module structure, port declarations, and data types (wire, reg, integer)

- Structural vs behavioural vs dataflow modelling styles

- Combinational logic: always blocks, assign statements, and operator precedence

- Blocking (=) vs non-blocking (<=) assignments — when each applies and why it matters for synthesis

- Gate-level primitives and their simulation behaviour

- Writing and running testbenches: stimulus generation and waveform interpretation

Recommended texts: Verilog HDL by Samir Palnitkar; Digital Design by Morris Mano and Michael Ciletti (Verilog edition).

Track 2: Sequential Logic, FSMs, and RTL Design

- D flip-flops, registers, and synchronous reset design

- Moore vs Mealy finite state machines — architecture, coding style, and output timing differences

- RTL design principles: separating combinational and sequential always blocks

- Counters, shift registers, and arithmetic units in synthesisable Verilog

- Clock domain crossing basics and synchronisation hazards

- Synthesis constraints: what gets inferred vs what needs explicit coding

- Common RTL anti-patterns that pass simulation but fail on FPGA hardware

Recommended texts: RTL Hardware Design Using VHDL by Pong P. Chu (RTL principles apply directly); Digital Design and Computer Architecture by Harris & Harris.

Track 3: FPGA Implementation and Advanced Verification

- Targeting Xilinx (Vivado) and Intel/Altera (Quartus) FPGA flows

- Timing analysis: setup and hold violations, critical path identification

- IP core integration and parameterised modules

- SystemVerilog extensions used in verification: interfaces, packages, enums

- Introduction to UVM-style thinking for graduate-level verification coursework

- FPGA resource utilisation reports: LUTs, FFs, BRAMs — reading and optimising

Recommended texts: FPGA Prototyping by Verilog Examples by Pong P. Chu; SystemVerilog for Verification by Chris Spear.

Platforms, Tools & Textbooks We Support

Verilog tutoring at MEB covers the full tool chain students encounter in real courses. Tutors work directly with your simulator and IDE — not a sanitised demo environment.

- Simulators: ModelSim / Questa, Icarus Verilog, Vivado Simulator, VCS

- FPGA IDEs: Xilinx Vivado Design Suite, Intel Quartus Prime

- Waveform viewers: GTKWave

- Online sandboxes: EDA Playground

- Version control: Git for HDL project workflows

- Related tools: Cadence Virtuoso for students bridging into ASIC design

What a Typical Verilog Session Looks Like

The tutor opens by checking what happened with the previous topic — usually a specific always block construct or FSM encoding the student was practising. From there, the session moves into the actual problem: the student shares their screen showing the Verilog code and the ModelSim or Vivado waveform. The tutor uses a digital pen-pad to annotate signal timelines and walk through exactly where the logic diverges from the intended behaviour. The student then rewrites the affected module while the tutor watches, asking questions rather than just correcting. Sessions close with one concrete task — usually a small design exercise or a targeted section of a past lab — and the next topic is flagged so the student knows what to review before the next session.

How MEB Tutors Help You with Verilog (The Learning Loop)

Diagnose: In the first session, the tutor identifies where the breakdown is — syntax confusion, simulation misreading, RTL-to-hardware misunderstanding, or FSM architecture errors. Most students come in thinking it’s a syntax problem. It usually isn’t.

Explain: The tutor works through a live example — your code or a clean version of the same concept — using a digital pen-pad to annotate timing diagrams and signal flow. No slides. No recorded lectures. Live problem, live explanation.

Practice: You attempt the next variation or module while the tutor stays present. The goal is for you to do the thinking — the tutor redirects, doesn’t replace.

Feedback: Every error gets a specific reason. “Your FSM output is wrong because the output logic is inside the sequential block — here’s why that causes a one-cycle delay.” Not just a correction. A reason that prevents the same error next time.

Plan: At the end of each session, the tutor sets the next topic and a realistic milestone. If you have an exam or lab in three weeks, that deadline drives the sequence.

Sessions run over Google Meet. The tutor uses a digital pen-pad or iPad with Apple Pencil to draw circuits, annotate waveforms, and mark up your code in real time. Before your first session, share your course syllabus or lab brief and any simulator output you’re stuck on. The first session is your diagnostic — the tutor uses it to map the plan. Start with the $1 trial — 30 minutes of live tutoring that also serves as your first diagnostic.

Try your first session for $1 — 30 minutes of live 1:1 tutoring or one homework question explained in full. No registration. No commitment. WhatsApp MEB now and get matched within the hour.

Tutor Match Criteria (How We Pick Your Tutor)

Not every electrical engineering tutor can teach Verilog well. MEB matches on specifics — not just subject area.

Subject depth: Tutors hold degrees in EE, computer engineering, or related fields and have demonstrable RTL design or FPGA implementation experience — not just HDL familiarity from a single course.

Tools: Every session runs over Google Meet with digital pen-pad or iPad and Apple Pencil — so timing diagrams and circuit annotations are live, not described verbally.

Time zone: Tutors are matched to your region — US, UK, Gulf, Canada, Australia — so session times are realistic, not 2 a.m. compromises.

Goals: Whether you need to pass a lab, close a conceptual gap before finals, or build a stronger foundation for graduate-level VLSI design, the tutor is selected for that specific outcome.

Unlike platforms where you fill out a form and wait, MEB responds in under a minute, 24/7. Tutor match takes under an hour. The $1 trial means you test before you commit. Everything runs over WhatsApp — no logins, no intake forms.

Students consistently tell us that the most useful thing about their first Verilog session was finding out what they didn’t know they didn’t know. The diagnostic isn’t a formality — it’s where the actual tutoring starts.

Study Plans (Pick One That Matches Your Goal)

After the diagnostic, the tutor builds a session sequence around your timeline. A catch-up plan (1–3 weeks) targets the specific gaps causing immediate lab or homework failures. An exam prep plan (4–8 weeks) structures revision through RTL concepts, FSM design, and FPGA implementation in order of exam weight. Weekly support runs alongside your semester, aligned to lab submission dates and coursework deadlines. The tutor maps the exact sequence after the first diagnostic session — nothing is pre-built, everything is calibrated to where you are right now.

Pricing Guide

Verilog tutoring starts at $20/hr for standard undergraduate HDL modules. Advanced RTL design, synthesis, and FPGA-level coursework typically falls in the $35–$70/hr range. Graduate-level support targeting ASIC design or research projects can reach $100/hr.

Rate factors: your course level, the complexity of the specific topics (basic combinational logic vs timing closure on FPGA), how tight your deadline is, and tutor availability at your preferred time zone.

For students targeting roles at semiconductor firms or pursuing graduate research in digital circuit design, tutors with professional RTL or FPGA industry backgrounds are available at higher rates — share your goal and MEB matches the tutor tier to your ambition.

Tutor availability compresses sharply in April–May and November–December during university exam periods. Book ahead if you’re working to a fixed submission date.

Start with the $1 trial — 30 minutes, no registration, no commitment. WhatsApp MEB for a quick quote.

MEB has served students in digital electronics, embedded systems, and Verilog across 18 years — the tutors know where students lose marks and exactly how to close those gaps before the next assessment.

Source: My Engineering Buddy, 2008–2025.

FAQ

Is Verilog hard to learn?

Verilog syntax is learnable quickly. The hard part is understanding concurrency — hardware runs in parallel, not sequentially like software. Blocking vs non-blocking assignments and FSM timing trip up most students. A tutor catches those mistakes before they become exam failures.

How many sessions will I need?

Most students see clear progress in 3–5 sessions. Closing a full semester’s gap before a lab deadline typically takes 8–12 focused hours. Graduate-level RTL or FPGA projects vary based on design complexity and how far into the project the student already is.

Can you help with homework and assignments?

Yes — MEB tutoring is guided learning. The tutor explains concepts, walks through the approach, and checks your reasoning. You understand the work, then submit it yourself. See our Academic Integrity policy and Why MEB page for full details on what we help with and what we don’t.

Will the tutor match my exact syllabus or exam board?

Yes. Before the first session, share your course outline, lab brief, or assignment spec. MEB matches a tutor who knows your specific simulator, FPGA platform, and course structure — not a generic HDL tutor who has to read your syllabus cold.

What happens in the first session?

The tutor runs a short diagnostic — identifying where your understanding breaks down and what the course expects. From that, they map the session sequence. If you have a submission in two weeks, the plan reflects that. No session is wasted on material you already know.

Is online Verilog tutoring as effective as in-person?

Yes, for HDL subjects specifically. Screen sharing means the tutor sees your exact code and simulator output. The digital pen-pad handles circuit annotation and waveform explanation in real time. Most students report that online sessions are more efficient — no commute, no scheduling friction.

What’s the difference between blocking and non-blocking assignments, and why do students always get this wrong?

Blocking (=) executes sequentially within an always block; non-blocking (<=) schedules assignments to update simultaneously at the end of the time step. Mixing them incorrectly inside sequential logic is the single most common Verilog mistake — a tutor identifies and fixes this pattern in the first session.

Can you help with Verilog for FPGA implementation, not just simulation?

Yes. MEB tutors cover the full flow — from RTL coding through synthesis, place-and-route, and timing analysis in Xilinx Vivado or Intel Quartus. If your design simulates correctly but fails on hardware, that’s a tutor session, not a documentation problem.

Do you cover SystemVerilog as well as Verilog?

Yes. Many graduate-level and advanced undergraduate courses now use SystemVerilog extensions for verification — interfaces, packages, and assertions. MEB tutors cover both. Specify which you need when you contact MEB and the match reflects that.

Can I get Verilog help at midnight or over the weekend?

Yes. MEB operates 24/7 across time zones. WhatsApp response averages under a minute regardless of hour. If you’re debugging a simulation at midnight before a 9 a.m. lab submission, that’s exactly when to reach out.

How do I get started?

Three steps: WhatsApp MEB, get matched to a verified Verilog tutor — usually within the hour — then start the $1 trial. Thirty minutes of live 1:1 tutoring or one homework question explained in full. No registration. No commitment.

Trust & Quality at My Engineering Buddy

Every MEB tutor goes through subject-specific screening before taking a student. That means a live demo session evaluated by MEB, verified academic credentials in electrical engineering or computer engineering, and demonstrated experience with Verilog — not just an HDL background in general. Ongoing session feedback is reviewed to ensure quality holds across every tutor. Rated 4.8/5 across 40,000+ verified reviews on Google.

MEB tutoring is guided learning — you understand the work, then submit it yourself. For full details on what we help with and what we don’t, read our Academic Integrity policy and Why MEB.

MEB has been running since 2008, serving 52,000+ students across the US, UK, Canada, Australia, Gulf, and Europe in 2,800+ subjects. Within electronics engineering, the platform covers Verilog alongside related subjects including digital signal processing and microprocessors — with tutors who know where the course difficulty actually sits, not where the syllabus claims it does. See how MEB structures sessions at our tutoring methodology page.

The tutors who teach Verilog at MEB have used it — in coursework, in research, and in industry. That’s the difference between explaining what an always block does and knowing which coding patterns break synthesis on a real FPGA target.

Source: My Engineering Buddy, 2008–2025.

A common pattern our tutors observe is that students who struggle with Verilog have never had the blocking vs non-blocking rule explained in terms of hardware behaviour — only in terms of syntax. Once that clicks, the whole language becomes more predictable and the simulation errors stop feeling random.

Explore Related Subjects

Students studying Verilog often also need support in:

- Analog Circuits

- Circuit Analysis

- Computer Engineering

- Integrated Circuits (IC)

- Logic Gates

- Microelectronics

- Signals and Systems

- Semiconductor Devices

Next Steps

Ready to stop guessing what your waveform is telling you?

- Share your course outline, simulator, and the specific topic or lab that’s blocking you

- Share your time zone and available session times

- MEB matches you with a verified Verilog tutor — usually within an hour

- First session starts with a diagnostic so every minute counts

Before your first session, have ready:

- Your course syllabus or lab brief

- A recent simulator output or homework problem you’re stuck on

- Your submission or exam date

The tutor handles the rest. Visit www.myengineeringbuddy.com for more on how MEB works.

WhatsApp to get started or email meb@myengineeringbuddy.com.

Reviewed by Subject Expert

This page has been carefully reviewed and validated by our subject expert to ensure accuracy and relevance.