Hire Verified & Experienced

VLSI design Tutors

4.8/5 40K+ session ratings collected on the MEB platform

Hire The Best VLSI design Tutor

Top Tutors, Top Grades. Without The Stress!

52,000+ Happy Students From Various Universities

How Much For Private 1:1 Tutoring & Hw Help?

Private 1:1 Tutoring and HW help Cost $20 – 35 per hour* on average.

Most students who fail VLSI design don’t fail because the physics is too hard — they fail because nobody walked them through timing closure or CMOS sizing at the moment it mattered.

VLSI Design Tutor Online

VLSI (Very Large Scale Integration) design is the process of creating integrated circuits by combining millions of transistors onto a single chip. It covers CMOS circuit design, digital logic, chip layout, timing analysis, and HDL-based implementation at undergraduate and graduate level.

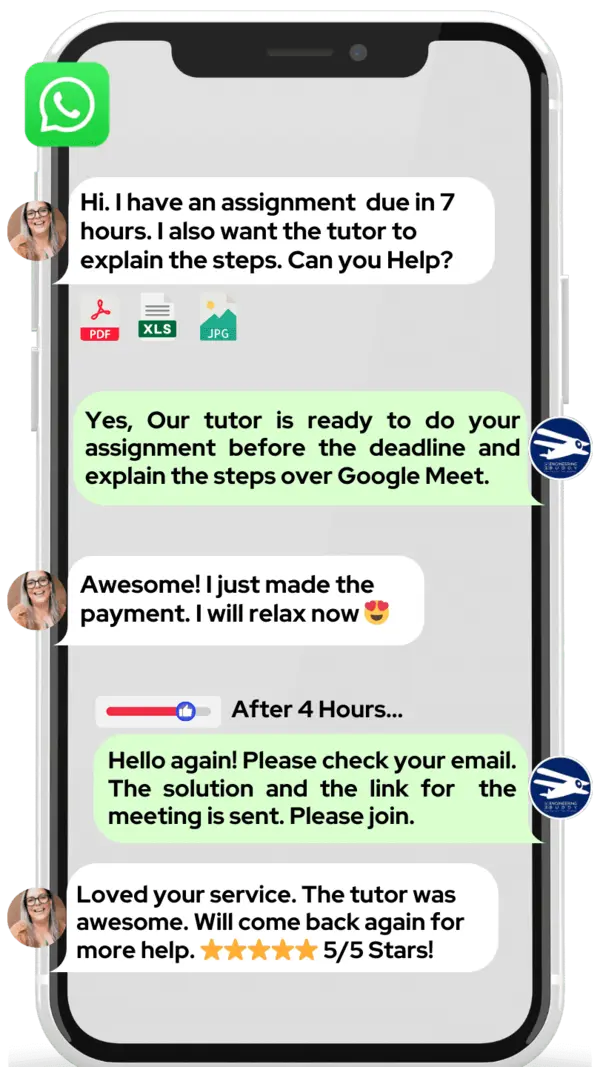

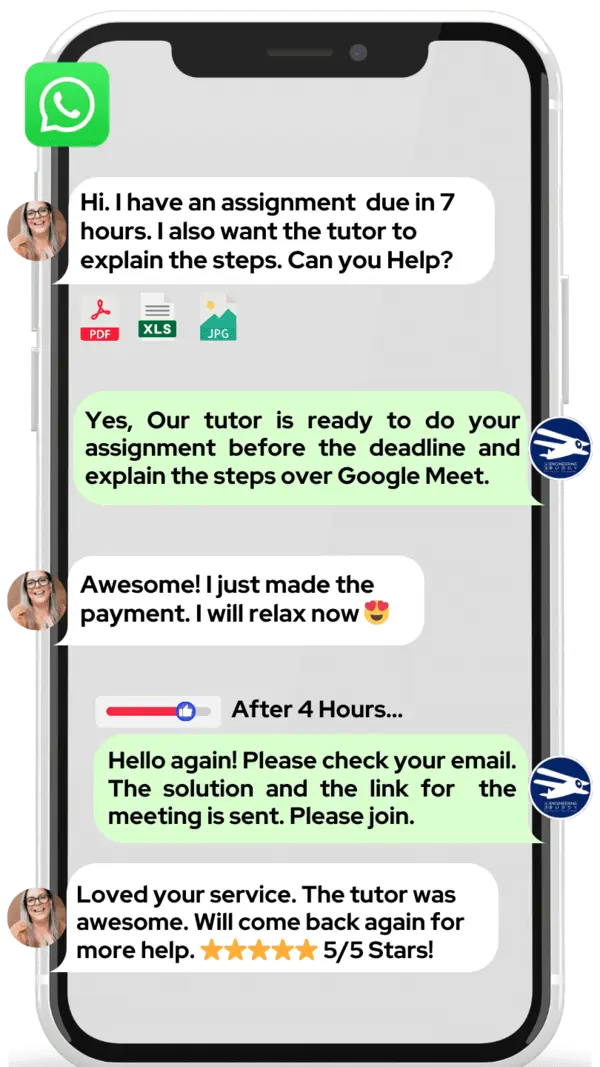

If you’ve searched for a VLSI design tutor near me, the good news is that location doesn’t matter here. MEB connects you with a 1:1 electrical engineering tutor who knows VLSI at the level your course demands — whether that’s CMOS inverter sizing, place-and-route, or full-custom layout in Cadence. Sessions run live over Google Meet, and your tutor adjusts to your exact syllabus from the first session.

- 1:1 online sessions tailored to your university course or research track

- Expert-verified tutors with graduate-level VLSI and semiconductor backgrounds

- Flexible time zones — US, UK, Canada, Australia, Gulf covered

- Structured learning plan built after a diagnostic session

- Ethical homework and assignment guidance — you understand before you submit

52,000+ students across the US, UK, Canada, Australia, and the Gulf have used MEB since 2008 — including students in Electrical Engineering subjects like VLSI design, analog circuits, and semiconductor devices.

Source: My Engineering Buddy, 2008–2025.

How Much Does a VLSI Design Tutor Cost?

Most VLSI design tutoring sessions run $20–$40/hr. Graduate-level work — think physical design, SPICE modelling at advanced nodes, or custom cell design — sits at $50–$100/hr depending on tutor depth. You can test the match before committing: the $1 trial gets you 30 minutes live or one homework problem explained in full.

| Level / Need | Typical Rate | What’s Included |

|---|---|---|

| Undergraduate VLSI modules | $20–$35/hr | 1:1 sessions, homework guidance |

| Graduate / Research-level | $35–$70/hr | Expert tutor, advanced EDA tools |

| $1 Trial | $1 flat | 30 min live session or 1 homework question |

Tutor availability tightens significantly around end-of-semester design project deadlines and final exam periods. Book early if your submission window is within four weeks.

WhatsApp MEB for a quick quote — average response time under 1 minute.

Who This VLSI Design Tutoring Is For

VLSI is one of those subjects where the gap between lecture slides and actual understanding can be enormous. Students often attend every class and still freeze when asked to size a CMOS gate or debug a timing violation in Cadence Virtuoso.

- Undergraduate EE students hitting the VLSI or microelectronics module for the first time

- Graduate students whose research involves chip design, mixed-signal circuits, or custom layout

- Students retaking after a failed first attempt — the conceptual gaps rarely fix themselves

- Students with a conditional offer to a Masters programme depending on this grade

- Students 4–6 weeks from finals with timing analysis, layout DRC, or HDL simulation still unresolved

- Students needing guided support on Cadence Virtuoso assignments or LTSpice-based design tasks

Students from programmes at Georgia Tech, Purdue, University of Michigan, Imperial College London, Delft University of Technology, KAIST, and the University of Toronto have worked with MEB tutors on VLSI coursework. Tutors understand what these programmes expect and how their marking schemes work.

1:1 Tutoring vs Self-Study vs AI vs YouTube vs Online Courses

Self-study works if you’re disciplined — but VLSI has too many tool-specific steps (DRC rules, netlist extraction, timing constraints) where a text explanation isn’t enough. AI tools answer fast but can’t watch you misroute a wire in Virtuoso and correct it live. YouTube covers inverter theory well; it stops when you hit your specific setup-time violation. Online courses give you structure but no one adjusts for the fact that your course uses a 180nm TSMC PDK while the video uses a generic model. A 1:1 VLSI design tutor works through your actual design files, your exact tool version, and your marking rubric — in real time.

Outcomes: What You’ll Be Able To Do in VLSI Design

After consistent 1:1 VLSI design tutoring, students can size CMOS transistors correctly for a target drive current and noise margin, analyze propagation delay through multi-stage logic chains, model and simulate circuit behaviour in SPICE before committing to layout, explain design rule violations and fix them without guessing, and present a complete RTL-to-GDSII flow in a viva or design review. These aren’t generic outcomes. They map directly to what examiners and research supervisors actually test.

Based on feedback from 40,000+ sessions collected by MEB from 2022 to 2025, 58% of students improved by one full grade after approximately 20 hours of 1:1 tutoring in subjects like VLSI design. A further 23% achieved at least a half-grade improvement.

Source: MEB session feedback data, 2022–2025.

At MEB, we’ve found that VLSI students who struggle with layout — DRC errors, LVS mismatches, parasitic extraction — almost always have a gap in their understanding of the device physics underneath. Fix that first, and the tool steps click into place within two or three sessions.

What We Cover in VLSI Design (Syllabus / Topics)

Track 1: CMOS Circuits and Device Physics

- MOS transistor operation — threshold voltage, overdrive, saturation

- CMOS inverter: DC characteristics, noise margins, switching threshold

- Transistor sizing for drive strength and propagation delay

- Pass transistors, transmission gates, and complementary CMOS logic

- Power dissipation — static, dynamic, and short-circuit components

- Body effect and its impact on threshold voltage in stacked devices

- SPICE-level simulation for DC, transient, and AC analysis

Key references: CMOS VLSI Design by Weste & Harris; Design of Analog CMOS Integrated Circuits by Razavi; Microelectronic Circuits by Sedra & Smith.

Track 2: Digital Logic Design and HDL Implementation

- Boolean algebra, Karnaugh maps, and combinational logic minimisation

- Sequential logic — flip-flops, latches, setup and hold time constraints

- Finite state machine design and state encoding strategies

- RTL design and synthesis using Verilog or VHDL

- Timing analysis — critical path, slack, clock skew, and timing closure

- FPGA prototyping and the differences from ASIC flows

- Simulation and testbench writing for functional verification

Key references: Digital Design and Computer Architecture by Harris & Harris; HDL Chip Design by Smith; RTL Hardware Design Using VHDL by Chu.

Track 3: Physical Design and Layout

- Standard cell layout — stick diagrams, Euler paths, CMOS layout rules

- Design rule check (DRC) and layout versus schematic (LVS) verification

- Floorplanning, placement, and routing in the ASIC flow

- Parasitic extraction and post-layout simulation

- Clock tree synthesis and power grid design

- Introduction to full-custom layout in Cadence Virtuoso or Magic VLSI

Key references: Layout Design in Integrated Circuit Design by Clein; CMOS VLSI Design by Weste & Harris (layout chapters); Static Timing Analysis for Nanometer Designs by Bhasker & Chadha.

Platforms, Tools & Textbooks We Support

VLSI design is heavily tool-dependent. MEB tutors work with students on the specific EDA platform their course uses, not a generic substitute. Tutors are familiar with Cadence Virtuoso (schematic entry, layout, Spectre simulation), LTSpice, Synopsys Design Compiler, Mentor Graphics, Magic VLSI, and Xilinx Vivado for FPGA design. If your course uses a specific PDK (TSMC 180nm, FreePDK45, or similar), share that before your first session.

- Cadence Virtuoso (Spectre, ADE, Layout Suite)

- LTSpice XVII

- Synopsys Design Compiler / PrimeTime

- Magic VLSI / OpenROAD (open-source flow)

- Xilinx Vivado / Intel Quartus (FPGA flows)

- ModelSim / QuestaSim (HDL simulation)

What a Typical VLSI Design Session Looks Like

The tutor opens by checking the previous topic — say, whether you were able to correctly size the pull-up network in last week’s NAND gate problem. Then you share your screen or design file. If it’s a CMOS circuit session, you and the tutor work through DC operating point analysis together: the tutor writes equations on the digital pen-pad, you replicate the steps and explain the logic back. If it’s layout, you walk through your DRC error list in Virtuoso while the tutor identifies which rules are violated and why. The session closes with a specific task — simulate the corrected circuit, fix two DRC errors, or write a testbench for a given FSM — and the next topic is agreed before you log off.

How MEB Tutors Help You with VLSI Design (The Learning Loop)

Diagnose: In the first session, the tutor asks you to walk through a recent problem — a circuit you couldn’t size, a timing error you couldn’t resolve. This surfaces whether the gap is in device physics, HDL syntax, tool workflow, or mathematical modelling. The rest of the plan follows from that.

Explain: The tutor works through problems live using a digital pen-pad — sketching transistor characteristics, annotating timing diagrams, or tracing signal paths through a schematic. You see the reasoning, not just the answer.

Practice: You attempt a similar problem while the tutor watches. This is where most of the learning actually happens. Errors surface immediately instead of at 2am before a deadline.

Feedback: The tutor corrects step-by-step — not just “this is wrong” but why the assumption broke down, which concept it links back to, and how an examiner or research supervisor would read the error.

Plan: At the end of each session, the tutor sets the next topic and a short practice task. Progress is tracked across sessions — not session-by-session guesswork.

Sessions run on Google Meet with a digital pen-pad or iPad and Apple Pencil. Before your first session, share your course syllabus, any past papers or assignments you’ve struggled with, and your exam or project deadline. The first session always starts with a diagnostic — no time wasted on topics you already understand. Start with the $1 trial — 30 minutes of live tutoring that also serves as your first diagnostic.

Students consistently tell us that the moment VLSI clicks is when they stop treating CMOS design as a set of rules to memorise and start treating it as a chain of physical trade-offs. That shift usually happens in one session — but only if someone is there to guide it.

Tutor Match Criteria (How We Pick Your Tutor)

Not every electrical engineer understands VLSI at the depth a graduate course demands. MEB matches on four criteria.

Subject depth: Tutors are vetted for the specific level — undergraduate device physics, RTL design, or graduate-level physical design. A tutor who excels at digital electronics is not automatically matched to a full-custom layout project.

Tools: Sessions run on Google Meet with a digital pen-pad or iPad and Apple Pencil. Tutors working on Cadence or Synopsys tool-heavy sessions are matched on tool familiarity, not just subject knowledge.

Time zone: Matched to your region — US, UK, Gulf, Canada, or Australia — so sessions run at hours that don’t destroy your sleep.

Goals: Whether you need exam scores, conceptual depth, homework completion, or support for a research project shapes who you get.

Unlike platforms where you fill out a form and wait, MEB responds in under a minute, 24/7. Tutor match takes under an hour. The $1 trial means you test before you commit. Everything runs over WhatsApp — no logins, no intake forms.

Study Plans (Pick One That Matches Your Goal)

After a diagnostic, the tutor maps a session plan to your timeline. A catch-up plan (1–3 weeks) targets the two or three concepts blocking your progress — timing analysis, CMOS sizing, or layout DRC — before a fast-approaching exam. An exam prep plan (4–8 weeks) works through the full syllabus systematically, with past paper practice in the final two weeks. Weekly support runs alongside your semester, aligned to coursework and lab submission deadlines so nothing is left to the last week. The tutor decides the sequence after the first session — not before.

Pricing Guide

VLSI design tutoring starts at $20/hr for standard undergraduate modules. Graduate-level work — physical design, mixed-signal circuits, advanced node device modelling — runs $50–$100/hr depending on tutor experience and subject depth.

Rate factors: your course level, topic complexity (basic inverter sizing versus full RTL-to-GDSII), how tight your timeline is, and tutor availability in your region.

Availability shrinks fast in the four weeks before final exams and major design project submissions. If your deadline is within a month, book now rather than later.

For students targeting roles at semiconductor companies or graduate programmes with strong chip design components, tutors with industry backgrounds in physical design or IC verification are available at higher rates — share your specific goal and MEB will match the tier to your ambition.

Start with the $1 trial — 30 minutes, no registration, no commitment. WhatsApp MEB for a quick quote.

MEB tutors have supported VLSI design students through everything from first-year integrated circuit modules to doctoral-level custom layout projects — with flexible rates that match the depth of what you actually need.

Source: My Engineering Buddy, 2008–2025.

FAQ

Is VLSI design hard?

Yes — it combines device physics, digital logic, HDL programming, and EDA tool workflows in one subject. Most students struggle where these areas intersect: for example, understanding why a timing constraint fails requires both circuit knowledge and tool familiarity simultaneously.

How many sessions are needed?

Students with a single concept gap — timing closure, CMOS sizing — typically need 4–6 sessions. Students who need structured exam prep or project support from scratch usually work over 10–20 sessions across a semester. The tutor gives a clearer estimate after the first diagnostic.

Can you help with homework and assignments?

MEB tutoring is guided learning — you understand the work, then submit it yourself. Tutors explain the method, walk you through similar problems, and check your reasoning — but do not complete submissions on your behalf. See our Academic Integrity policy and Why MEB page for full details on what we help with and what we don’t.

Will the tutor match my exact syllabus or exam board?

Yes. Share your university, course code, and syllabus document before the first session. MEB matches tutors who know that specific syllabus or, for less common ones, tutors who review it in advance so the first session is already calibrated to your actual course content.

What happens in the first session?

The tutor runs a short diagnostic — asking you to work through a recent problem or explain a concept you found difficult. This reveals where the gap actually is, which shapes every session that follows. No time is spent on topics you already understand.

Is online tutoring as effective as in-person?

For VLSI design, often more so. Screen sharing lets you show your actual Cadence layout or SPICE netlist. The tutor annotates directly on a digital pen-pad. You can share your exact design file rather than describing a problem verbally. Tool-specific issues are easier to debug live than in a classroom.

What is the difference between VLSI and FPGA design, and do MEB tutors cover both?

VLSI refers to custom or semi-custom IC design targeting fabrication — the full ASIC flow. FPGA design uses a programmable hardware platform rather than fabricating a chip. Many courses cover both. MEB tutors can support FPGA design and VLSI separately or together depending on your course structure.

My course uses Cadence Virtuoso and I’ve never used it before — can a tutor help me learn the tool alongside the theory?

Yes. This is one of the most common requests MEB receives for VLSI. Tutors walk through schematic entry, simulation setup in ADE, and layout steps in the same session where the circuit theory is covered — so you’re not learning the tool in isolation from the concepts it’s implementing.

Can I get VLSI design help at midnight or over a weekend?

Yes. MEB operates across time zones and responds on WhatsApp within minutes, 24/7. Late-night sessions are common for students in the US and Gulf working to a same-day deadline. Share your availability and MEB matches a tutor who works those hours.

What if I don’t get along with my assigned tutor?

Tell MEB on WhatsApp and a replacement is arranged — usually the same day. The $1 trial is specifically designed so you test the match before spending anything significant. Most mismatches are caught at the trial stage.

Do you offer group VLSI design sessions?

MEB’s model is 1:1 only. Group sessions are not offered. Every session is built around one student’s specific gaps, tool setup, and deadline — group formats don’t allow for that level of calibration in a subject as tool-intensive and conceptually layered as VLSI design.

How do I get started?

Three steps: WhatsApp MEB with your course name and deadline, get matched to a verified tutor within the hour, then start with the $1 trial — 30 minutes live or one problem explained in full. No registration required.

Trust & Quality at My Engineering Buddy

Every MEB tutor goes through subject-specific vetting — not a generic teaching test. For VLSI design, that means verifying graduate-level knowledge of CMOS circuits, HDL design, and at least one major EDA tool. Tutors complete a live demo session before being matched to students, and ongoing session feedback is reviewed regularly. Rated 4.8/5 across 40,000+ verified reviews on Google.

MEB tutoring is guided learning — you understand the work, then submit it yourself. For full details on what we help with and what we don’t, read our Academic Integrity policy and Why MEB.

MEB has served 52,000+ students across the US, UK, Canada, Australia, the Gulf, and Europe since 2008 — across 2,800+ subjects. In Electrical Engineering, that includes students working on microelectronics courses, digital signal processing, and analog electronics alongside VLSI design. The platform has been operating continuously since 2008 — not a startup with six months of data. See our tutoring methodology for how sessions are structured.

The Institute of Electrical and Electronics Engineers (IEEE) remains the primary professional body setting standards for IC design practice and education — MEB tutors working in VLSI design hold membership or are familiar with IEEE design standards relevant to their coursework support.

Source: IEEE, 2024.

A common pattern our tutors observe is that VLSI students spend weeks re-reading lecture notes without testing their understanding on actual tool output. One session where you run a simulation, read the waveforms, and explain what they mean is worth more than five hours of passive review.

Explore Related Subjects

Students studying VLSI design often also need support in:

- Analog Signal Processing

- Circuit Design

- MOSFET

- Digital Circuit

- Electronic Circuit Design

- Signals and Systems

- Microprocessors

- Embedded Systems

Next Steps

When you WhatsApp MEB, have these ready: your university, course name or code, the topics you’re stuck on, and your exam or project deadline date. Share your time zone and weekly availability so the match is practical from day one.

- Bring your exam board and syllabus, or your course outline if no formal exam

- Bring a recent assignment or past paper problem you couldn’t complete

- Bring your deadline — the tutor builds the session plan around it

MEB matches you with a verified VLSI design tutor within the hour. The first session starts with a diagnostic so no time is wasted on topics you already have covered. Visit www.myengineeringbuddy.com for more on how MEB works.

WhatsApp to get started or email meb@myengineeringbuddy.com.

Reviewed by Subject Expert

This page has been carefully reviewed and validated by our subject expert to ensure accuracy and relevance.